# HDL Coder™ Reference

**R**2014**b**

# MATLAB®

### How to Contact MathWorks

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

#### HDL Coder™ Reference

© COPYRIGHT 2013–2014 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| March 2013     | Online only | New for Version 3.2 (R2013a)            |

|----------------|-------------|-----------------------------------------|

| September 2013 | Online only | Revised for Version 3.3 (R2013b)        |

| March 2014     | Online only | Revised for Version 3.4 (Release 2014a) |

| October 2014   | Online only | Revised for Version 3.5 (Release 2014b) |

# Contents

**Supported Blocks**

**Properties** — Alphabetical List

Class reference for HDL code generation from Simulink

Function Reference for HDL Code Generation from MATLAB

> Class Reference for HDL Code Generation from MATLAB

Shared Class and Function Reference for HDL Code Generation from MATLAB and Simulink

1

2

3

4

6

7

# Functions – Alphabetical List

# checkhdl

Check subsystem or model for HDL code generation compatibility

# **Syntax**

```

checkhdl(bdroot)

checkhdl('dut')

checkhdl(gcb)

output = checkhdl('system')

```

# Description

checkhdl generates an HDL Code Generation Check Report, saves the report to the target folder, and displays the report in a new window. Before generating HDL code, use checkhdl to check your subsystems or models.

The report lists compatibility errors with a link to each block or subsystem that caused a problem. To highlight and display incompatible blocks, click each link in the report while keeping the model open.

The report file name is *system\_*report.html. *system* is the name of the subsystem or model passed in to checkhdl.

When a model or subsystem passes checkhdl, that does not imply code generation will complete. checkhdl does not verify all block parameters.

checkhdl(bdroot) examines the current model for HDL code generation compatibility.

checkhdl('*dut*') examines the specified DUT model name, model reference name, or subsystem name with full hierarchical path.

checkhdl(gcb) examines the currently selected subsystem.

```

output = checkhdl('system')

```

does not generate a report. Instead, it returns a 1xN struct array with one entry for each error, warning, or message. *system* specifies a model or the full block path for a subsystem at any level of the model hierarchy.

checkhdl reports three levels of compatibility problems:

- *Errors*: cause the code generation process to terminate. The report must not contain errors to continue with HDL code generation.

- *Warnings*: indicate problems in the generated code, but allow HDL code generation to continue.

- *Messages*: indication that some data types have special treatment. For example, the HDL Coder<sup>™</sup> software automatically converts single-precision floating-point data types to double-precision because VHDL<sup>®</sup> and Verilog<sup>®</sup> do not support single-precision data types.

### **Examples**

Check the subsystem symmetric\_fir within the model sfir\_fixed for HDL code generation compatibility and generate a compatibility report.

```

checkhdl('sfir_fixed/symmetric_fir')

```

Check the subsystem symmetric\_fir\_err within the model sfir\_fixed\_err for HDL code generation compatibility, and return information on problems encountered in the struct output.

```

output = checkhdl('sfir_fixed_err/symmetric_fir_err')

### Starting HDL Check.

...

### HDL Check Complete with 4 errors, warnings and messages.

```

The following  $MATLAB^{\ensuremath{\mathbb{R}}}$  commands display the top-level structure of the struct output, and its first cell.

```

output =

1x4 struct array with fields:

path

type

message

level

output(1)

ans =

path: 'sfir_fixed_err/symmetric_fir_err/Product'

type: 'block'

message: 'Unhandled mixed double and non-double datatypes at ports of block'

level: 'Error'

```

### See Also

makehdl

### Tutorials

• "Selecting and Checking a Subsystem for HDL Compatibility"

# hdladvisor

Display HDL Workflow Advisor

# **Syntax**

```

hdladvisor(gcb)

hdladvisor(subsystem)

hdladvisor(model,'SystemSelector')

```

# Description

hdladvisor(gcb) starts the HDL Workflow Advisor, passing the currently selected subsystem within the current model as the DUT to be checked.

hdladvisor(*subsystem*) starts the HDL Workflow Advisor, passing in the path to a specified subsystem within the model.

hdladvisor(*model*, 'SystemSelector') opens a System Selector window that lets you select a subsystem to be opened into the HDL Workflow Advisor as the device under test (DUT) to be checked.

# Examples

Open the subsystem <code>symmetric\_fir</code> within the model <code>sfir\_fixed</code> into the HDL Workflow Advisor.

```

hdladvisor('sfir_fixed/symmetric_fir')

```

Open a System Selector window to select a subsystem within the current model. Then open the selected subsystem into the HDL Workflow Advisor.

```

hdladvisor(gcs,'SystemSelector')

```

# Alternatives

You can also open the HDL Workflow Advisor from the your model window by selecting Code > HDL Code > HDL Workflow Advisor.

### See Also

"What Is the HDL Workflow Advisor?" | "Using the HDL Workflow Advisor Window"

# hdlcoder.optimizeDesign

Automatic iterative HDL design optimization

# **Syntax**

```

hdlcoder.optimizeDesign(model, optimizationCfg)

hdlcoder.optimizeDesign(model, cpGuidanceFile)

```

# Description

hdlcoder.optimizeDesign(model, optimizationCfg) automatically optimizes your generated HDL code based on the optimization configuration you specify.

hdlcoder.optimizeDesign(model, cpGuidanceFile) regenerates the optimized HDL code without rerunning the iterative optimization, by using data from a previous run of hdlcoder.optimizeDesign.

# Examples

#### Maximize clock frequency

Maximize the clock frequency for a model, **sfir\_fixed**, by performing up to 10 optimization iterations.

Open the model and specify the DUT subsystem.

```

model = 'sfir_fixed';

dutSubsys = 'symmetric_fir';

open_system(model);

hdlset_param(model,'HDLSubsystem',[model,'/',dutSubsys]);

```

Set your synthesis tool and target device options.

Enable HDL test bench generation.

```

hdlset param(model,'GenerateHDLTestBench','on');

```

Save your model.

You must save your model if you want to regenerate code later without rerunning the iterative optimizations, or resume your run if it is interrupted. When you use hdlcoder.optimizeDesign to regenerate code or resume an interrupted run, HDL Coder checks the model checksum and generates an error if the model has changed.

Create an optimization configuration object, **OC**.

```

oc = hdlcoder.OptimizationConfig;

```

Set the iteration limit to 10.

oc.IterationLimit = 10;

Optimize the model.

hdlcoder.optimizeDesign(model,oc)

```

hdlset_param('sfir_fixed', 'HDLSubsystem', 'sfir_fixed/symmetric_fir');

hdlset_param('sfir_fixed', 'SynthesisTool', 'Xilinx ISE');

hdlset_param('sfir_fixed', 'SynthesisToolChipFamily', 'Zynq');

hdlset_param('sfir_fixed', 'SynthesisToolDeviceName', 'xc7z030');

hdlset_param('sfir_fixed', 'SynthesisToolPackageName', 'fbg484');

hdlset param('sfir fixed', 'SynthesisToolSpeedValue', '-3');

Iteration 0

Generate and synthesize HDL code ...

(CP ns) 16.26 (Constraint ns) 5.85 (Elapsed s) 143.66 Iteration 1

Generate and synthesize HDL code ...

(CP ns) 16.26 (Constraint ns) 5.85 (Elapsed s) 278.72 Iteration 2

Generate and synthesize HDL code ...

(CP ns) 10.25 (Constraint ns) 12.73 (Elapsed s) 427.22 Iteration 3

Generate and synthesize HDL code ...

(CP ns) 9.55 (Constraint ns) 9.73 (Elapsed s) 584.37 Iteration 4

Generate and synthesize HDL code ...

(CP ns) 9.55 (Constraint ns) 9.38 (Elapsed s) 741.04 Iteration 5

Generate and synthesize HDL code ...

Exiting because critical path cannot be further improved.

Summary report: summary.html

Achieved Critical Path (CP) Latency : 9.55 ns Elapsed : 741.04 s

```

```

Iteration 0: (CP ns) 16.26 (Constraint ns) 5.85 (Elapsed s) 143.66

Iteration 1: (CP ns) 16.26 (Constraint ns) 5.85 (Elapsed s) 278.72

Iteration 2: (CP ns) 10.25 (Constraint ns) 12.73 (Elapsed s) 427.22

Iteration 3: (CP ns) 9.55 (Constraint ns) 9.73 (Elapsed s) 584.37

Iteration 4: (CP ns) 9.55 (Constraint ns) 9.38 (Elapsed s) 741.04

Final results are saved in

/tmp/hdlsrc/sfir_fixed/hdlexpl/Final-07-Jan-2014-17-04-41

Validation model: gm sfir fixed vnl

```

Then HDL Coder stops after five iterations because the fourth and fifth iterations had the same critical path, which indicates that the coder has found the minimum critical path. The design's maximum clock frequency after optimization is 1 / 9.55 ns, or 104.71 MHz.

#### Optimize for specific clock frequency

Optimize a model, sfir\_fixed, to a specific clock frequency, 50 MHz, by performing up to 10 optimization iterations, and do not generate an HDL test bench.

Open the model and specify the DUT subsystem.

```

model = 'sfir_fixed';

dutSubsys = 'symmetric_fir';

open_system(model);

hdlset_param(model,'HDLSubsystem',[model,'/',dutSubsys]);

```

Set your synthesis tool and target device options.

```

hdlset_param (model,'SynthesisTool','Xilinx ISE', ...

'SynthesisToolChipFamily','Zynq', ...

'SynthesisToolDeviceName','xc7z030', ...

'SynthesisToolPackageName','fbg484', ...

'SynthesisToolSpeedValue','-3')

```

Disable HDL test bench generation.

```

hdlset param(model,'GenerateHDLTestBench','off');

```

Save your model.

You must save your model if you want to regenerate code later without rerunning the iterative optimizations, or resume your run if it is interrupted. When you use hdlcoder.optimizeDesign to regenerate code or resume an interrupted run, HDL Coder checks the model checksum and generates an error if the model has changed. Create an optimization configuration object, oc.

```

oc = hdlcoder.OptimizationConfig;

```

Configure the automatic iterative optimization to stop after it reaches a clock frequency of 50MHz, or 10 iterations, whichever comes first.

```

oc.ExplorationMode = ...

hdlcoder.OptimizationConfig.ExplorationMode.TargetFrequency;

oc.TargetFrequency = 50;

oc.IterationLimit = 10; =

```

Optimize the model.

```

hdlcoder.optimizeDesign(model,oc)

```

```

hdlset_param('sfir_fixed', 'GenerateHDLTestBench', 'off');

hdlset_param('sfir_fixed', 'HDLSubsystem', 'sfir_fixed/symmetric_fir');

hdlset_param('sfir_fixed', 'SynthesisTool', 'Xilinx ISE');

hdlset_param('sfir_fixed', 'SynthesisToolChipFamily', 'Zynq');

hdlset_param('sfir_fixed', 'SynthesisToolDeviceName', 'xc7z030');

hdlset_param('sfir_fixed', 'SynthesisToolPackageName', 'fbg484');

hdlset_param('sfir_fixed', 'SynthesisToolSpeedValue', '-3');

```

```

Iteration 0

Generate and synthesize HDL code ...

(CP ns) 16.26 (Constraint ns) 20.00 (Elapsed s) 134.02 Iteration 1

Generate and synthesize HDL code ...

Exiting because constraint (20.00 ns) has been met (16.26 ns).

Summary report: summary.html

Achieved Critical Path (CP) Latency : 16.26 ns Elapsed : 134.02 s

Iteration 0: (CP ns) 16.26 (Constraint ns) 20.00 (Elapsed s) 134.02

Final results are saved in

/tmp/hdlsrc/sfir_fixed/hdlexpl/Final-07-Jan-2014-17-07-14

Validation model: gm_sfir_fixed_vnl

```

Then HDL Coder stops after one iteration because it has achieved the target clock frequency. The critical path is 16.26 ns, a clock frequency of 61.50 GHz.

#### Resume clock frequency optimization using saved data

Run additional optimization iterations for a model, sfir\_fixed, using saved iteration data, because you terminated in the middle of a previous run.

Open the model and specify the DUT subsystem.

```

model = 'sfir_fixed';

dutSubsys = 'symmetric_fir';

open_system(model);

hdlset param(model,'HDLSubsystem',[model,'/',dutSubsys]);

```

Set your synthesis tool and target device options to the same values as in the interrupted run.

```

hdlset_param (model,'SynthesisTool','Xilinx ISE', ...

'SynthesisToolChipFamily','Zynq', ...

'SynthesisToolDeviceName','xc7z030', ...

'SynthesisToolPackageName','fbg484', ...

'SynthesisToolSpeedValue','-3')

```

Enable HDL test bench generation.

hdlset\_param(model,'GenerateHDLTestBench','on');

Create an optimization configuration object, **OC**.

oc = hdlcoder.OptimizationConfig;

Configure the automatic iterative optimization to run using data from the first iteration of a previous run.

oc.ResumptionPoint = 'Iter5-07-Jan-2014-17-04-29';

Optimize the model.

```

hdlcoder.optimizeDesign(model,oc)

```

```

hdlset_param('sfir_fixed', 'HDLSubsystem', 'sfir_fixed/symmetric_fir');

hdlset_param('sfir_fixed', 'SynthesisTool', 'Xilinx ISE');

hdlset_param('sfir_fixed', 'SynthesisToolChipFamily', 'Zynq');

hdlset_param('sfir_fixed', 'SynthesisToolDeviceName', 'xc7z030');

hdlset_param('sfir_fixed', 'SynthesisToolPackageName', 'fbg484');

hdlset_param('sfir_fixed', 'SynthesisToolSpeedValue', '-3');

Try to resume from resumption point: Iter5-07-Jan-2014-17-04-29

Iteration 5

Generate and synthesize HDL code ...

Exiting because critical path cannot be further improved.

Summary report: summary.html

Achieved Critical Path (CP) Latency : 9.55 ns Elapsed : 741.04 s

Iteration 0: (CP ns) 16.26 (Constraint ns) 5.85 (Elapsed s) 143.66

```

```

Iteration 1: (CP ns) 16.26 (Constraint ns) 5.85 (Elapsed s) 278.72

```

```

Iteration 2: (CP ns) 10.25 (Constraint ns) 12.73 (Elapsed s) 427.22

Iteration 3: (CP ns) 9.55 (Constraint ns) 9.73 (Elapsed s) 584.37

Iteration 4: (CP ns) 9.55 (Constraint ns) 9.38 (Elapsed s) 741.04

Final results are saved in

/tmp/hdlsrc/sfir_fixed/hdlexpl/Final-07-Jan-2014-17-07-30

Validation model: gm_sfir_fixed_vnl

```

Then coder stops after one additional iteration because it has achieved the target clock frequency. The critical path is 9.55 ns, or a clock frequency of 104.71 MHz.

#### Regenerate code using original design and saved optimization data

Regenerate HDL code using the original model, **sfir\_fixed**, and saved data from the final iteration of a previous optimization run.

Open the model and specify the DUT subsystem.

```

model = 'sfir_fixed';

dutSubsys = 'symmetric_fir';

open_system(model);

hdlset param(model,'HDLSubsystem',[model,'/',dutSubsys]);

```

Set your synthesis tool and target device options to the same values as in the original run.

```

hdlset_param (model,'SynthesisTool','Xilinx ISE', ...

'SynthesisToolChipFamily','Zynq', ...

'SynthesisToolDeviceName','xc7z030', ...

'SynthesisToolPackageName','fbg484', ...

'SynthesisToolSpeedValue','-3')

```

Regenerate HDL code using saved optimization data from cpGuidance.mat.

```

hdlcoder.optimizeDesign(model,

'hdlsrc/sfir_fixed/hdlexpl/Final-19-Dec-2013-23-05-04/cpGuidance.mat')

Final results are saved in

/tmp/hdlsrc/sfir_fixed/hdlexpl/Final-07-Jan-2014-17-16-52

Validation model: gm sfir fixed vnl

```

### **Input Arguments**

model — Model name

string

Model name, specified as a string.

Example: 'sfir\_fixed'

#### optimizationCfg — Optimization configuration

hdlcoder.OptimizationConfig

Optimization configuration, specified as an hdlcoder.OptimizationConfig object.

#### cpGuidanceFile — File containing saved optimization data

'' (default) | string

File that contains saved data from the final optimization iteration, including relative path, specified as a string. Use this file to regenerate optimized code without rerunning the iterative optimization.

The file name is cpGuidance.mat. You can find the file in the iteration folder name that starts with Final, which is a subfolder of hdlexpl.

Example: 'hdlexpl/Final-11-Dec-2013-23-17-10/cpGuidance.mat'

# More About

"Automatic Iterative Optimization"

### See Also

**Classes** hdlcoder.OptimizationConfig

Functions hdlcoder.supportedDevices

#### **Properties**

SynthesisTool | SynthesisToolChipFamily | SynthesisToolDeviceName | SynthesisToolPackageName | SynthesisToolSpeedValue

# hdlcoder.supportedDevices

Show supported target hardware and device details

# **Syntax**

hdlcoder.supportedDevices

# Description

hdlcoder.supportedDevices shows a link to a report that contains device and device property names for target devices supported by your synthesis tool.

You can use the supported target device information to set SynthesisToolChipFamily, SynthesisToolDeviceName, SynthesisToolPackageName, and SynthesisToolSpeedValue for your model.

To see the report link, you must have a synthesis tool set up. If you have more than one synthesis tool available, you see a different report link for each synthesis tool.

# **Examples**

#### Set the target device for your model

In this example, you set the target device for a model, sfir\_fixed. Two synthesis tools are available, Altera<sup>®</sup> Quartus II and Xilinx<sup>®</sup> ISE. The target device is a Xilinx Virtex-6 XC6VLX130T FPGA.

Show the supported target device reports.

hdlcoder.supportedDevices

Altera QUARTUS II Device List Xilinx ISE Device List

Click the Xilinx ISE Device List link to open the supported target device report and view details for your target device.

Open the model, sfir\_fixed.

sfir\_fixed

Set the SynthesisToolChipFamily, SynthesisToolDeviceName, SynthesisToolPackageName, and SynthesisToolSpeedValue model parameters based on details from the supported target device report.

View the nondefault parameters for your model, including target device information.

#### hdldispmdlparams

| SynthesisTool            | 1 | 'Xilinx ISE' |

|--------------------------|---|--------------|

| SynthesisToolChipFamily  | : | 'Virtex6'    |

| SynthesisToolDeviceName  | : | 'xc6vlx130t' |

| SynthesisToolPackageName | 1 | 'ff484'      |

| SynthesisToolSpeedValue  | : | - 1          |

### More About

• "Synthesis Tool Path Setup"

#### See Also

SynthesisToolChipFamily | SynthesisToolDeviceName |

SynthesisToolPackageName | SynthesisToolSpeedValue

# hdldispblkparams

Display HDL block parameters with nondefault values

# **Syntax**

```

hdldispblkparams(path)

hdldispblkparams(path,'all')

```

# Description

hdldispblkparams(path) displays, for the specified block, the names and values of HDL parameters that have nondefault values.

hdldispblkparams(path, 'all') displays, for the specified block, the names and values of all HDL block parameters.

# **Input Arguments**

path

Path to a block or subsystem in the current model.

Default: None

#### 'all'

If you pass in the string 'all', hdldispblkparams displays the names and values of all HDL properties of the specified block.

# **Examples**

The following example displays nondefault HDL block parameter settings for a Sum of Elements block).

hdldispblkparams('simplevectorsum/vsum/Sum of Elements')

Implementation

Architecture : Linear

Implementation Parameters

InputPipeline : 1

The following example displays HDL block parameters and values for the currently selected block, (a Sum of Elements block).

hdldispblkparams(gcb,'all')

Implementation

Architecture : Linear

Implementation Parameters

InputPipeline : 0

OutputPipeline : 0

#### See Also

"Set and View HDL Block Parameters"

# hdldispmdlparams

Display HDL model parameters with nondefault values

# **Syntax**

```

hdldispmdlparams(model)

hdldispmdlparams(model,'all')

```

# Description

hdldispmdlparams(model) displays, for the specified model, the names and values of HDL parameters that have nondefault values.

hdldispmdlparams(model, 'all') displays the names and values of all HDL parameters for the specified model.

# **Input Arguments**

model

Name of an open model.

#### Default: None

#### 'all'

If you pass in the string <code>'all'</code> , <code>hdldispmdlparams</code> displays the names and values of all HDL properties of the specified model.

# **Examples**

The following example displays HDL properties of the current model that have nondefault values.

hdldispmdlparams(bdroot)

HDL CodeGen Parameters (non-default)

| CodeGenerationOutput<br>HDLSubsystem | : 'GenerateHDLCodeAndDisplayGeneratedModel'<br>: 'simplevectorsum 2atomics/Subsystem' |

|--------------------------------------|---------------------------------------------------------------------------------------|

| OptimizationReport                   | : 'on'                                                                                |

| ResetInputPort                       | : 'rst'                                                                               |

| ResetType                            | : 'Synchronous'                                                                       |

The following example displays HDL properties and values of the current model.

hdldispmdlparams(bdroot,'all')

HDL CodeGen Parameters

| AddPipelineRegisters<br>Backannotation<br>BlockGenerateLabel<br>CheckHDL<br>ClockEnableInputPort | : 'off'<br>: 'on'<br>: '_gen'<br>: 'off'<br>: 'clk_enable' |

|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| VerilogFileExtension                                                                             | : '.v'                                                     |

### See Also

"View HDL Model Parameters"

# hdlget\_param

Return value of specified HDL block-level parameter for specified block

# **Syntax**

p = hdlget\_param(block\_path,prop)

# Description

p = hdlget\_param(block\_path,prop) gets the value of a specified HDL property of a block or subsystem, and returns the value to the output variable.

# Input Arguments

#### block\_path

Path to a block or subsystem in the current model.

#### Default: None

#### prop

A string designating one of the following:

- The name of an HDL block property of the block or subsystem specified by block\_path.

- 'all' : If prop is set to 'all', hdlget\_param returns Name, Value pairs for HDL properties of the specified block.

#### Default: None

# **Output Arguments**

#### р

p receives the value of the HDL block property specified by prop. The data type and dimensions of p depend on the data type and dimensions of the value returned. If prop is set to 'all', p is a cell array.

# **Examples**

In the following example hdlget\_param returns the value of the HDL block parameter OutputPipeline to the variable p.

```

p = hdlget_param(gcb,'OutputPipeline')

p =

3

```

In the following example  $hdlget_param$  returns HDL block parameters and values for the current block to the cell array p.

# More About

#### Tips

• Use hdlget\_param only to obtain the value of HDL block parameters (see "HDL Block Properties" for a list of block implementation parameters). Use hdldispmdlparams to see the values of HDL model parameters. To obtain the value of general model parameters, use the get\_param function.

#### See Also

hdlset\_param | hdlsaveparams | hdlrestoreparams

# hdllib

Create library of blocks that support HDL code generation

# **Syntax**

```

hdllib

hdllib('html')

```

# Description

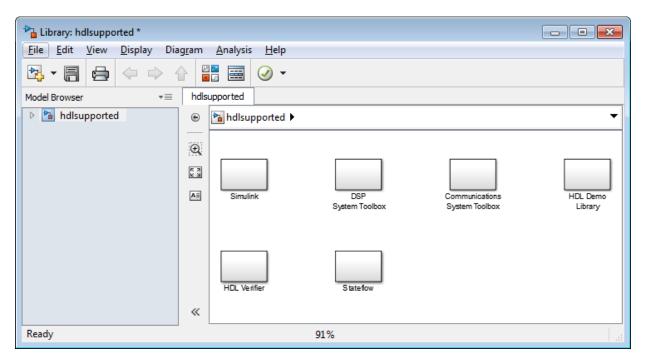

hdllib creates a library of blocks that are compatible with HDL code generation. Use blocks from this library to build models that are compatible with the HDL Coder software.

The default library name is hdlsupported. After you generate the library, you can save it to a folder of your choice.

Regenerate the library each time you install a new release to keep it current.

hdllib('html') creates a library of blocks that are compatible with HDL code generation, and generates two additional HTML reports: a categorized list of blocks (hdlblklist.html), and a table of blocks and their HDL code generation parameters (hdlsupported.html).

# Examples

#### Create a supported blocks library

To create a library that contains blocks supported for HDL code generation:

hdllib

The hdlsupported block library opens.

#### Create a supported blocks library and HTML reports

To create a library and HTML reports showing blocks supported for HDL code generation:

#### hdllib('html')

### HDL supported block list hdlblklist.html

### HDL implementation list hdlsupported.html

The hdlsupported library opens. To view the reports, click the hdlblklist.html and hdlsupported.html links.

# hdlrestoreparams

Restore block- and model-level HDL parameters to model

# **Syntax**

```

hdlrestoreparams(dut)

hdlrestoreparams(dut,filename)

```

# Description

hdlrestoreparams(dut) restores to the specified model the default block- and modellevel HDL settings.

hdlrestoreparams(dut,filename) restores to the specified model the block- and model-level HDL settings from a previously saved file.

# Examples

#### **Reset and Restore HDL-Related Model Parameters**

Open the model.

sfir\_fixed

Verify that model parameters have default values.

hdlsaveparams('sfir\_fixed/symmetric\_fir')

hdlset\_param('sfir\_fixed', 'HDLSubsystem', 'sfir\_fixed');

Set HDL-related model parameters for the symmetric\_fir subsystem.

Verify that model parameters are set.

```

hdlsaveparams('sfir_fixed/symmetric_fir')

```

Save the model parameters to a MATLAB script, sfir\_saved\_params.m.

Reset HDL-related model parameters to default values.

hdlrestoreparams('sfir\_fixed/symmetric\_fir')

Verify that model parameters have default values.

```

hdlsaveparams('sfir fixed/symmetric fir')

```

Restore the saved model parameters from sfir\_saved\_params.m.

Verify that the saved model parameters are restored.

```

hdlsaveparams('sfir_fixed/symmetric_fir')

```

#### Input Arguments

dut — DUT subsystem name string

#### DUT subsystem name, specified as a string, with full hierarchical path.

Example: 'modelname/subsysTarget'

Example: 'modelname/subsysA/subsysB/subsysTarget'

filename — Name of file

string

Name of file containing previously saved HDL model parameters.

Example: 'mymodel\_saved\_params.m'

See Also hdlsaveparams

# hdlsaveparams

Save nondefault block- and model-level HDL parameters

# **Syntax**

```

hdlsaveparams(dut)

hdlsaveparams(dut,filename)

```

# **Description**

hdlsaveparams(dut) displays nondefault block- and model-level HDL parameters.

hdlsaveparams(dut,filename) saves nondefault block- and model-level HDL parameters to a MATLAB script.

# **Examples**

#### **Display HDL-Related Nondefault Model Parameters**

Open the model.

sfir\_fixed

Set HDL-related model parameters for the symmetric\_fir subsystem.

```

hdlset_param('sfir_fixed/symmetric_fir', 'SharingFactor', 3)

hdlset_param('sfir_fixed/symmetric_fir/Product', 'InputPipeline', 5)

```

$Display \ HDL-related \ nondefault \ model \ parameters \ for \ the \ \texttt{symmetric\_fir} \ subsystem.$

hdlsaveparams('sfir\_fixed/symmetric\_fir')

```

hdlset_param('sfir_fixed', 'HDLSubsystem', 'sfir_fixed/symmetric_fir');

hdlset_param('sfir_fixed/symmetric_fir', 'SharingFactor', 3);

hdlset param('sfir fixed/symmetric fir/Product', 'InputPipeline', 5);

```

The output identifies the subsystem and displays its HDL-related parameter values.

#### Save and Restore HDL-Related Model Parameters

Open the model.

sfir\_fixed

Verify that model parameters have default values.

```

hdlsaveparams('sfir fixed/symmetric fir')

```

```

hdlset_param('sfir_fixed', 'HDLSubsystem', 'sfir_fixed');

```

Set HDL-related model parameters for the symmetric\_fir subsystem.

Verify that model parameters are set.

Save the model parameters to a MATLAB script, sfir\_saved\_params.m.

Reset HDL-related model parameters to default values.

```

hdlrestoreparams('sfir_fixed/symmetric_fir')

```

Verify that model parameters have default values.

```

hdlsaveparams('sfir_fixed/symmetric_fir')

```

Restore the saved model parameters from sfir\_saved\_params.m.

Verify that the saved model parameters are restored.

### **Input Arguments**

dut – DUT subsystem name

string

DUT subsystem name, specified as a string, with full hierarchical path.

Example: 'modelname/subsysTarget'

Example: 'modelname/subsysA/subsysB/subsysTarget'

#### filename - Name of file

string

Name of file to which you are saving model parameters, specified as a string.

Example: 'mymodel\_saved\_params.m'

See Also hdlrestoreparams

# hdlset\_param

Set HDL-related parameters at model or block level

# **Syntax**

```

hdlset_param(path,Name,Value)

```

# Description

hdlset\_param(path,Name,Value) sets HDL-related parameters in the block or model referenced by path. The parameters to be set, and their values, are specified by one or more Name,Value pair arguments. You can specify several name and value pair arguments in any order as Name1,Value1,...,NameN,ValueN.

# **Input Arguments**

#### path

Path to the model or block for which hdlset\_param is to set one or more parameter values.

#### Default: None

#### **Name-Value Pair Arguments**

Specify optional comma-separated pairs of Name,Value arguments, where Name is the argument name and Value is the corresponding value. Name must appear inside single quotes (' '). You can specify several name and value pair arguments in any order as Name1,Value1,...,NameN,ValueN.

#### 'Name'

Name is a string specifying the name of one of the following:

• A model-level HDL-related property. See Properties — Alphabetical List for a list of model-level properties, their data types and their default values.

• An HDL block property, such as an implementation name or an implementation parameter. See "HDL Block Properties" for a list of block implementation parameters.

#### Default: None

#### 'Value'

Value is a value to be applied to the corresponding property in a Name, Value argument.

Default: Default value is dependent on the property.

### **Examples**

The following example uses the sfir\_fixed model to demonstrate how to locate a group of blocks in a subsystem and specify the same output pipeline depth for each of the blocks.

```

open sfir_fixed;

prodblocks = find_system('sfir_fixed/symmetric_fir', 'BlockType', 'Product');

for ii=1:length(prodblocks), hdlset_param(prodblocks{ii}, 'OutputPipeline', 2), end;

```

### **More About**

#### Tips

- When you set multiple parameters on the same model or block, use a single hdlset\_param command with multiple pairs of arguments, rather than multiple hdlset\_param commands. This technique is more efficient because using a single call requires evaluating parameters only once.

- To set HDL block parameters for multiple blocks, use the find\_system function to locate the blocks of interest. Then, use a loop to iterate over the blocks and call hdlset\_param to set the desired parameters.

- "Set and View HDL Block Parameters"

- "Set HDL Block Parameters for Multiple Blocks"

### See Also

hdlget\_param | hdlsaveparams | hdlrestoreparams

# hdlsetup

Set up model parameters for HDL code generation

## **Syntax**

```

hdlsetup('modelname')

```

## Description

hdlsetup('modelname') sets the parameters of the model specified by modelname to common default values for HDL code generation. After using hdlsetup, you can use set\_param to modify these default settings.

Open the model before you invoke the hdlsetup command.

To see which model parameters are affected by hdlsetup, open hdlsetup.m.

### How hdlsetup Configures Solver Options

hdlsetup configures Solver options used by HDL Coder. These options are:

• Type: Fixed-step. This is the recommended solver type for most HDL applications.

HDL Coder also supports variable-step solvers under the following conditions:

- The device under test (DUT) is single-rate.

- The sample times of all signals driving the DUT are greater than 0.

- Solver: Discrete (no continuous states). You can use other fixed-step solvers, but this option is usually best for simulating discrete systems.

- Tasking mode: SingleTasking. HDL Coder does not support multitasking mode.

Do not set **Tasking mode** to Auto.

# makehdl

Generate HDL RTL code from model, subsystem, or model reference

# **Syntax**

```

makehdl(dut)

makehdl(dut,Name,Value)

```

# Description

makehdl(dut) generates HDL code from the specified DUT model, subsystem, or model

reference.

makehdl(dut,Name,Value) generates HDL code from the specified DUT model, subsystem, or model reference with options specified by one or more name-value pair arguments.

# Examples

### Generate VHDL for the Current Model

Generate VHDL code for the current model.

Generate HDL code for the current model with code generation options set to default values.

```

makehdl(bdroot)

```

The generated VHDL code is saved in the hdlsrc folder.

### Generate Verilog for a Subsystem Within a Model

Generate Verilog for the subsystem symmetric\_fir within the model sfir\_fixed.

Open the sfir\_fixed model.

#### sfir\_fixed;

The model opens in a new Simulink window.

#### Generate Verilog for the symmetric\_fir subsystem.

```

makehdl('sfir_fixed/symmetric_fir', 'TargetLanguage', 'Verilog')

```

```

### Generating HDL for 'sfir_fixed/symmetric_fir'.

### Starting HDL check.

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings,

and 0 messages.

### Begin Verilog Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as

hdlsrc\sfir_fixed\symmetric_fir.v

### HDL code generation complete.

```

The generated Verilog code for the symmetric\_fir subsystem is saved in hdlsrc \sfir\_fixed\symmetric\_fir.v.

Close the model.

bdclose('sfir\_fixed');

### Check Subsystem for Compatibility with HDL Code Generation

Check that the subsystem <code>symmetric\_fir</code> is compatible with HDL code generation, then generate HDL.

Open the sfir\_fixed model.

sfir\_fixed;

The model opens in a new Simulink window.

Check the symmetric\_fir subsystem for compatibility with HDL code generation. Generate code with code generation options set to default values.

makehdl('sfir\_fixed/symmetric\_fir','CheckHDL','on')

The generated VHDL code for the symmetric\_fir subsystem is saved in hdlsrc \sfir\_fixed\symmetric\_fir.vhd.

Close the model.

bdclose('sfir\_fixed');

## **Input Arguments**

#### dut - DUT model or subsystem name

string

DUT model or subsystem name, specified as subsystem name, top-level model name, or model reference name with full hierarchical path.

```

Example: 'top_level_name'

Example: 'top level name/subsysA/subsysB/codegen subsys name'

```

### **Name-Value Pair Arguments**

Specify optional comma-separated pairs of Name,Value arguments. Name is the argument name and Value is the corresponding value. Name must appear inside single quotes (' '). You can specify several name and value pair arguments in any order as Name1,Value1,...,NameN,ValueN.

```

Example: 'TargetLanguage', 'Verilog'

```

## **Basic Options**

```

'TargetLanguage' — Target language

'VHDL'(default) | 'Verilog'

```

For more information, see "TargetLanguage".

```

'TargetDirectory' - Output directory

'hdlsrc' (default) | string

```

For more information, see "TargetDirectory".

```

'CheckHDL' — Check HDL code generation compatibility

'off' (default) | 'on'

```

For more information, see "CheckHDL\_property".

```

'GenerateHDLCode' — Generate HDL code

```

'on' (default) | 'off'

For more information, see "GenerateHDLCode".

'SplitEntityArch' — Split VHDL entity and architecture into separate files 'off' (default) | 'on'

For more information, see "SplitEntityArch".

```

'Verbosity' — Level of message detail

1 (default) | 0

```

For more information, see "Verbosity".

### **Report Generation**

```

'HDLCodingStandard' — Specify HDL coding standard string

```

For more information, see "HDLCodingStandard".

```

'HDLCodingStandardCustomizations' — Specify HDL coding standard customization object

hdlcoder.CodingStandard object

```

For more information, see "HDLCodingStandardCustomizations".

```

'Traceability' — Generate report with mapping links between HDL and model

'off' (default) | 'on'

```

For more information, see "Traceability".

```

'ResourceReport' — Resource utilization report generation 'off' (default) | 'on'

```

For more information, see "ResourceReport".

```

<code>'OptimizationReport' — Optimization report generation</code> <code>'off' (default) | 'on'</code>

```

For more information, see "OptimizationReport".

'GenerateWebview' — Include model Webview 'on' (default) | 'off'

For more information, see "GenerateWebview".

### Speed and Area Optimization

```

'BalanceDelays' — Delay balancing

'on' (default) | 'off'

```

For more information, see "BalanceDelays".

# 'DistributedPipeliningPriority' — Specify priority for distributed pipelining algorithm

'NumericalIntegrity' (default) | 'Performance'

For more information, see DistributedPipeliningPriority.

# 'HierarchicalDistPipelining' — Hierarchical distributed pipelining 'off' (default) | 'on'

For more information, see "HierarchicalDistPipelining".

```

' <code>PreserveDesignDelays</code> ' — Prevent distributed pipelining from moving design delays ' <code>off'</code> (default) | ' <code>on'</code>

```

For more information, see PreserveDesignDelays.

# 'ClockRatePipelining' — Insert pipeline registers at the clock rate instead of the data rate for multi-cycle paths

'on' (default) | 'off'

For more information, see ClockRatePipelining.

'MaxOversampling' — Limit the maximum sample rate 0 (default) | N, where N is an integer greater than 1

For more information, see "MaxOversampling".

'MaxComputationLatency' — Specify the maximum number of time steps for which your DUT inputs are guaranteed to be stable

1 (default) | N, where N is an integer greater than 1

For more information, see "MaxComputationLatency".

'MinimizeClockEnables' — Omit clock enable logic for single-rate designs

For more information, see "MinimizeClockEnables".

'RAMMappingThreshold' — Minimum RAM size for mapping to RAMs instead of registers 256 (default) | positive integer

The minimum RAM size required for mapping to RAMs instead of registers, specified in bits.

For more information, see "RAMMappingThreshold".

'HighlightFeedbackLoops' — Highlight feedback loops inhibiting delay balancing and optimizations

```

'off' (default) | 'on'

```

For more information, see HighlightFeedbackLoops.

'HighlightFeedbackLoopsFile' — Feedback loop highlighting script file name

'highlightFeedbackLoop' (default) | string

For more information, see HighlightFeedbackLoopsFile.

### **Coding Style**

'UserComment' — HDL file header comment string

For more information, see "UserComment".

```

'UseAggregatesForConst' — Represent constant values with aggregates 'off' (default) | 'on'

```

For more information, see "UseAggregatesForConst".

# 'UseRisingEdge' — Use VHDL rising\_edge or falling\_edge function to detect clock transitions

'off' (default) | 'on'

For more information, see "UseRisingEdge".

```

<code>'LoopUnrolling'</code> — Unroll VHDL FOR and GENERATE loops <code>'off'</code> (default) <code>| 'on'</code>

```

For more information, see "LoopUnrolling".

```

'UseVerilogTimescale' — Generate 'timescale compiler directives

'on' (default) | 'off'

```

For more information, see "UseVerilogTimescale".

```

'InlineConfigurations' - Include VHDL configurations

'on' (default) | 'off'

```

For more information, see "InlineConfigurations".

```

'SafeZeroConcat' — Type-safe syntax for concatenated zeros 'on' (default) \mid 'off'

```

For more information, see "SafeZeroConcat".

```

'DateComment' — Include time stamp in header 'on' (default) | 'off'

```

For more information, see "DateComment".

```

'ScalarizePorts' — Flatten vector ports into scalar ports 'off' (default) | 'on'

```

For more information, see "ScalarizePorts".

```

'MinimizeIntermediateSignals' — Minimize intermediate signals

'off' (default) | 'on'

```

For more information, see "MinimizeIntermediateSignals".

```

'RequirementComments' — Link from code generation reports to requirement documents ' on ' (default) | ' off'

```

For more information, see "RequirementComments".

```

'InlineMATLABBlockCode' — Inline HDL code for MATLAB Function blocks

```

For more information, see "InlineMATLABBlockCode".

'MaskParameterAsGeneric' – Reusable code generation for subsystems with identical mask parameters 'off' (default) | 'on'

For more information, see "MaskParameterAsGeneric".

'InitializeBlockRAM' — Initial signal value generation for RAM blocks

'on' (default) | 'off'

For more information, see "InitializeBlockRAM".

'RAMArchitecture' - RAM architecture

'WithClockEnable' (default) | 'WithoutClockEnable'

For more information, see "RAMArchitecture".

```

'HandleAtomicSubsystem' — Reusable code generation for identical atomic subsystems 'on' (default) | 'off'

```

For more information, see "HandleAtomicSubsystem".

### **Clocks and Reset**

'ClockEdge' — Active clock edge

'Rising' (default) | 'Falling'

For more information, see "ClockEdge".

'ClockInputs' — Single or multiple clock inputs

'Single' (default) | 'Multiple'

Single or multiple clock inputs, specified as a string.

For more information, see "ClockInputs".

### 'Oversampling' — Oversampling factor for global clock

1 (default) | integer greater than or equal to 0

Frequency of global oversampling clock, specified as an integer multiple of the model's base rate.

For more information, see "Oversampling".

```

'ResetAssertedLevel' - Asserted (active) level of reset

'active-high' (default) | 'active-low'

```

For more information, see "ResetAssertedLevel".

```

'ResetType' - Reset type

'async' (default) | 'sync'

```

For more information, see "ResetType".

```

'TriggerAsClock' — Use trigger signal as clock in triggered subsystems

'off' (default) | 'on'

```

For more information, see TriggerAsClock.

```

'TimingControllerArch' — Generate reset for timing controller

'default' (default) | 'resettable'

```

For more information, see TimingControllerArch.

## Test Bench

```

'Verbosity' — Level of message detail

0 (default) | n

```

For more information, see "Verbosity".

```

'GenerateCoSimBlock' - Generate HDL Cosimulation block

```

'off' (default) | 'on'

Generate an HDL Cosimulation block so you can simulate the DUT in  $\mathsf{Simulink}^{\circledast}$  with an HDL simulator.

For more information, see "GenerateCoSimBlock".

'GenerateCoSimModel' - Generate HDL Cosimulation model

'ModelSim' (default) | 'Incisive'

Generate a model containing an HDL Cosimulation block for the specified HDL simulator.

For more information, see "GenerateCoSimModel".

'GenerateValidationModel' - Generate validation model

'off' (default) | 'on'

For more information, see "GenerateValidationModel".

'SimulatorFlags' — Options for generated compilation scripts string

For more information, see "SimulatorFlags".

'TestBenchReferencePostFix' - Suffix for test bench reference signals

' ref' (default) | string

For more information, see "TestBenchReferencePostFix".

### **Script Generation**

<code>'EDAScriptGeneration'</code> — Enable or disable script generation for third-party tools <code>'on'</code> (default) <code>| 'off'</code>

For more information, see "EDAScriptGeneration".

'HDLCompileInit' - Compilation script initialization string

'vlib work\n' (default) | string

For more information, see "HDLCompileInit".

'HDLCompileTerm' - Compilation script termination string

'' (default) | string

For more information, see "HDLCompileTerm".

'HDLCompileFilePostfix' — Postfix for compilation script file name

'\_compile.do' (default) | string

For more information, see "HDLCompileFilePostfix".

```

'HDLCompileVerilogCmd' - Verilog compilation command

'vlog %s %s\n' (default) | string

```

Verilog compilation command, specified as a string. The SimulatorFlags name-value pair specifies the first argument, and the module name specifies the second argument.

For more information, see "HDLCompileVerilogCmd".

```

'HDLCompileVHDLCmd' - VHDL compilation command

'vcom %s %s\n' (default) | string

```

VHDL compilation command, specified as a string. The SimulatorFlags name-value pair specifies the first argument, and the entity name specifies the second argument.

For more information, see "HDLCompileVerilogCmd".

```

'HDLLintTool' — HDL lint tool

'None' (default) | 'AscentLint' | 'Leda' | 'SpyGlass' | 'Custom'

```

HDL lint tool, specified as a string.

For more information, see "HDLLintTool".

#### 'HDLLintInit' — HDL lint initialization string

string

HDL lint initialization, specified as a string. The default is derived from the HDLLintTool name-value pair.

For more information, see "HDLLintInit".

### 'HDLLintCmd' — HDL lint command

string

HDL lint command, specified as a string. The default is derived from the HDLLintTool name-value pair.

For more information, see "HDLLintCmd".

'HDLLintTerm' — HDL lint termination string

HDL lint termination, specified as a string. The default is derived from the HDLLintTool name-value pair.

For more information, see "HDLLintTerm".

#### 'HDLSynthTool' — Synthesis tool

```

'None'(default)|'ISE'|'Libero'|'Precision'|'Quartus'|'Synplify'|

'Vivado'|'Custom'

```

HDL synthesis tool, specified as a string.

For more information, see "HDLSynthTool".

#### 'HDLSynthCmd' — HDL synthesis command

string

HDL synthesis command, specified as a string. The default is derived from the HDLSynthTool name-value pair.

For more information, see "HDLSynthCmd".

### 'HDLSynthFilePostfix' — Postfix for synthesis script file name

string

HDL synthesis script file name postfix, specified as a string. The default is derived from the HDLSynthTool name-value pair.

For more information, see "HDLSynthFilePostfix".

### 'HDLSynthInit' — Synthesis script initialization string

string

Initialization for the HDL synthesis script, specified as a string. The default is derived from the HDLSynthTool name-value pair.

For more information, see "HDLSynthInit".

### 'HDLSynthTerm' — Synthesis script termination string

string

Termination string for the HDL synthesis script. The default is derived from the HDLSynthTool name-value pair.

For more information, see "HDLSynthTerm".

## **Generated Model**

'CodeGenerationOutput' — Display and generation of generated model 'GenerateHDLCode' (default) | 'GenerateHDLCodeAndDisplayGeneratedModel' | 'DisplayGeneratedModelOnly'

For more information, see "CodeGenerationOutput".

'GeneratedModelName' — Generated model name same as original model name (default) | string

For more information, see "GeneratedModelName".

### 'GeneratedModelNamePrefix' - Prefix for generated model name

'gm\_' (default) | string

For more information, see "GeneratedModelNamePrefix".

'HighlightAncestors' — Highlight parent blocks of generated model blocks differing from original model

'on' (default) | 'off'

For more information, see "HighlightAncestors".

```

'HighlightColor' — Color of highlighted blocks in generated model

'cyan' (default) | 'yellow' | 'magenta' | 'red' | 'green' | 'blue' | 'white' |

'magenta' | 'black'

```

For more information, see "HighlightColor".

## **Synthesis**

```

'SynthesisTool' — Synthesis tool

''(default) | 'Altera Quartus II' | 'Xilinx ISE' | 'Xilinx Vivado'

```

For more information, see "SynthesisTool".

```

'MulticyclePathInfo' — Multicycle path constraint file generation

```

For more information, see "MulticyclePathInfo".

### Port Names and Types

'ClockEnableInputPort' - Clock enable input port name

'clk enable' (default) | string

Clock enable input port name, specified as a string.

For more information, see "ClockEnableInputPort".

'ClockEnableOutputPort' - Clock enable output port name

'ce out' (default) | string

Clock enable output port name, specified as a string.

For more information, see "ClockEnableOutputPort".

### 'ClockInputPort' - Clock input port name

'Clk' (default) | string

Clock input port name, specified as a string.

For more information, see "ClockInputPort".

```

'InputType' — HDL data type for input ports

'wire' or 'std_logic_vector' (default) | 'signed/unsigned'

```

HDL data type for input ports, specified as a string.

VHDL inputs can have 'std\_logic\_vector' or 'signed/unsigned' data type. Verilog inputs must be 'wire'.

For more information, see "InputType".

#### 'OutputType' — HDL data type for output ports

```

'Same as input data type' (default) | 'std_logic_vector' | 'signed/

unsigned' | 'wire'

```

HDL data type for output ports, specified as a string.

VHDL output can be 'Same as input data type', 'std\_logic\_vector' or 'signed/unsigned'. Verilog output must be 'wire'.

For more information, see "OutputType".

```

'ResetInputPort' - Reset input port name

'reset' (default) | string

```

Reset input port name, specified as a string.

For more information, see "ResetInputPort".

### File and Variable Names

'VerilogFileExtension' - Verilog file extension

'.v' (default) | string

For more information, see "VerilogFileExtension".

# 'VHDLFileExtension' - VHDL file extension '.vhd' (default) | string

For more information, see "VHDLFileExtension".

'VHDLArchitectureName' — VHDL architecture name 'rtl' (default) | string

For more information, see "VHDLArchitectureName".

'VHDLLibraryName' — VHDL library name 'work' (default) | string

For more information, see "VHDLLibraryName".

'SplitEntityFilePostfix' - Postfix for VHDL entity file names

'\_entity' (default) | string

For more information, see "SplitEntityFilePostfix".

#### 'SplitArchFilePostfix' — Postfix for VHDL architecture file names

'\_arch' (default) | string

For more information, see "SplitArchFilePostfix".

'PackagePostfix' - Postfix for package file name

' pkg' (default) | string

For more information, see "PackagePostfix".

'HDLMapFilePostfix' - Postfix for mapping file

' map.txt' (default) | string

For more information, see "HDLMapFilePostfix".

'BlockGenerateLabel' — Block label postfix for VHDL GENERATE statements

'\_gen' (default) | string

For more information, see "BlockGenerateLabel".

'ClockProcessPostfix' — Postfix for clock process names

'\_process' (default) | string

For more information, see "ClockProcessPostfix".

'ComplexImagPostfix' - Postfix for imaginary part of complex signal

'\_im' (default) | string

For more information, see "ComplexImagPostfix".

'ComplexRealPostfix' - Postfix for imaginary part of complex signal names

'\_re' (default) | string

For more information, see "ComplexRealPostfix".

'EntityConflictPostfix' — Postfix for duplicate VHDL entity or Verilog module names

'\_block' (default) | string

For more information, see "EntityConflictPostfix".

'InstanceGenerateLabel' — Instance section label postfix for VHDL GENERATE statements

'\_gen' (default) | string

For more information, see "InstanceGenerateLabel".

'InstancePostfix' - Postfix for generated component instance names

'' (default) | string

For more information, see "InstancePostfix".

'InstancePrefix' — Prefix for generated component instance names 'u ' (default) | string

For more information, see "InstancePrefix".

'OutputGenerateLabel' — Output assignment label postfix for VHDL GENERATE statements 'outputgen' (default) | string

ourpurgen (derault) | string

For more information, see "OutputGenerateLabel".

'PipelinePostfix' - Postfix for input and output pipeline register names

' pipe' (default) | string

For more information, see "PipelinePostfix".

'ReservedWordPostfix' — Postfix for names conflicting with VHDL or Verilog reserved words

'\_rsvd' (default) | string

For more information, see "ReservedWordPostfix".

'TimingControllerPostfix' - Postfix for timing controller name

' tc' (default) | string

For more information, see "TimingControllerPostfix".

'VectorPrefix' - Prefix for vector names

'vector of ' (default) | string

For more information, see "VectorPrefix".

'EnablePrefix' - Prefix for internal enable signals

'enb' (default) | string

Prefix for internal clock enable and control flow enable signals, specified as a string.

For more information, see "EnablePrefix".

### 'ModulePrefix' - Prefix for modules or entity names

'' (default) | string

Specify a prefix for every module or entity name in the generated HDL code. HDL Coder also applies this prefix to generated script file names

For more information, see "ModulePrefix".

See Also

checkhdl | makehdltb

# makehdltb

Generate HDL test bench from model or subsystem

# **Syntax**

```

makehdltb(dut)

makehdltb(dut,Name,Value)

```

# Description

${\tt makehdltb(dut)}$  generates an HDL test bench from the specified subsystem or model reference.

makehdltb(dut,Name,Value) generates an HDL test bench from the specified subsystem or model reference with options specified by one or more name-value pair arguments.

# Examples

### Generate VHDL Test Bench

Generate VHDL DUT and test bench for a subsystem.

Use makehdl to generate VHDL code for the subsystem symmetric\_fir.

```

makehdl('sfir_fixed/symmetric_fir')

```

```

### Generating HDL for 'sfir_fixed/symmetric_fir'.

### Starting HDL check.

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings,

and 0 messages.

### Begin VHDL Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as

hdlsrc\sfir_fixed\symmetric_fir.vhd

### HDL code generation complete.

```

After makehdl is complete, use makehdltb to generate a VHDL test bench for the same subsystem.

```

makehdltb('sfir_fixed/symmetric_fir')

```

```

### Begin TestBench generation.

### Generating HDL TestBench for 'sfir_fixed/symmetric_fir'.

### Begin simulation of the model 'gm_sfir_fixed'...

### Collecting data...

### Generating test bench: hdlsrc\sfir_fixed\symmetric_fir_tb.vhd

### Creating stimulus vectors...

### HDL TestBench generation complete.

The generated VHDL test bench code is saved in the hdlsrc folder.

```

#### **Generate Verilog Test Bench**

Generate Verilog DUT and test bench for a subsystem.

Use makehdl to generate Verilog code for the subsystem symmetric\_fir.

```

makehdl('sfir_fixed/symmetric_fir','TargetLanguage','Verilog')

### Generating HDL for 'sfir_fixed/symmetric_fir'.

### Starting HDL check.

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings,

and 0 messages.

### Begin Verilog Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as

hdlsrc\sfir_fixed\symmetric_fir.v

### HDL code generation complete.

```

After makehdl is complete, use makehdltb to generate a Verilog test bench for the same subsystem.

```

makehdltb('sfir_fixed/symmetric_fir', 'TargetLanguage', 'Verilog')

```

```

### Begin TestBench generation.

### Generating HDL TestBench for 'sfir_fixed/symmetric_fir'.

### Begin simulation of the model 'gm_sfir_fixed'...

### Collecting data...

### Generating test bench: hdlsrc\sfir_fixed\symmetric_fir_tb.v

### Creating stimulus vectors...

### HDL TestBench generation complete.

```

The generated Verilog test bench code is saved in the hdlsrc\sfir\_fixed folder.

### **Input Arguments**

### dut - DUT subsystem or model reference name

string

DUT subsystem or model reference name, specified as a string, with full hierarchical path.

```

Example: 'modelname/subsysTarget'

```

Example: 'modelname/subsysA/subsysB/subsysTarget'

### **Name-Value Pair Arguments**

Specify optional comma-separated pairs of Name,Value arguments. Name is the argument name and Value is the corresponding value. Name must appear inside single quotes (' '). You can specify several name and value pair arguments in any order as Name1,Value1,...,NameN,ValueN.

```

Example: 'TargetLanguage', 'Verilog'

```

## **Basic Options**

```

'TargetLanguage' — Target language

'VHDL'(default) | 'Verilog'

```

For more information, see "TargetLanguage".

# 'TargetDirectory' - Output directory 'hdlsrc' (default) | string

For more information, see "TargetDirectory".

```

'SplitEntityArch' — Split VHDL entity and architecture into separate files 'off' (default) | 'on'

```

For more information, see "SplitEntityArch".

## Test Bench

```

'ForceClock' - Force clock input

```

'on' (default) | 'off'

Specify that the generated test bench drives the clock enable input based on ClockLowTime and ClockHighTime.

For more information, see "ForceClock".

# **'ClockHighTime'** – Clock high time 5 (default) | positive integer

Clock high time during a clock period, specified in nanoseconds.

For more information, see "ClockHighTime".

'ClockLowTime' - Clock low time 5 (default) | positive integer

Clock low time during a clock period, specified in nanoseconds.

For more information, see "ClockLowTime".

'ForceClockEnable' - Force clock enable input

'on' (default) | 'off'

Specify that the generated test bench drives the clock enable input.

For more information, see "ForceClockEnable".

```

'ClockInputs' - Single or multiple clock inputs

'Single' (default) | 'Multiple'

```

Single or multiple clock inputs, specified as a string.

For more information, see "ClockInputs".

```

'ForceReset' - Force reset input

'on' (default) | 'off'

```

Specify that the generated test bench drives the reset input.

For more information, see "ForceReset".

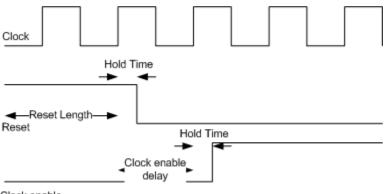

### 'ResetLength' — Reset asserted time length

$2 \ (default) \ | \ integer greater than or equal to <math display="inline">0$

Length of time that reset is asserted, specified as the number of clock cycles.

For more information, see "ResetLength".

```

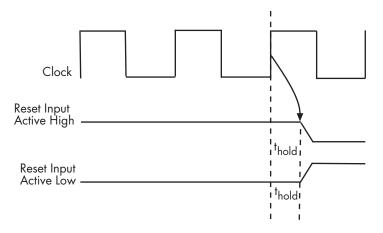

'ResetAssertedLevel' - Asserted (active) level of reset

'active-high' (default) | 'active-low'

```

For more information, see "ResetAssertedLevel".

```

<code>'HoldInputDataBetweenSamples'</code> — Hold valid data for signals clocked at slower rate <code>'on'</code> (default) <code>| 'off'</code>

```

For more information, see "HoldInputDataBetweenSamples".

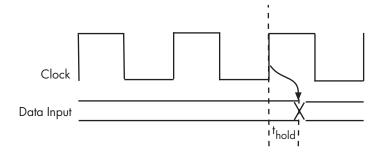

### 'HoldTime' — Hold time for inputs and forced reset

2 (default) | positive integer

Hold time for inputs and forced reset, specified in nanoseconds.

For more information, see "HoldTime".

```

' IgnoreDataChecking ' — Time to wait after clock enable before checking output data 0 (default) | positive integer

```

Time after clock enable is asserted before starting output data checks, specified in number of samples.

For more information, see "IgnoreDataChecking".

#### 'InitializeTestBenchInputs' — Initialize test bench inputs to 0 'off' (default) | 'on'

For more information, see "InitializeTestBenchInputs".

# <code>'MultifileTestBench'</code> — Divide generated test bench into helper functions, data, and HDL test bench files

'off' (default) | 'on'

For more information, see "MultifileTestBench".

#### 'UseFileI0InTestBench' — Use file I/O to read/write test bench data

'off' (default) | 'on'

For more information, see "UseFileIOInTestBench".

# 'TestBenchClockEnableDelay' — Number of clock cycles between deassertion of reset and assertion of clock enable

1 (default) | positive integer

For more information, see "TestBenchClockEnableDelay".

```

'TestBenchDataPostFix' — Postfix for test bench data file name

```

```

'_data' (default) | string

```

For more information, see "TestBenchDataPostFix".

'TestBenchPostFix' — Suffix for test bench name

' tb' (default) | string

For more information, see "TestBenchPostFix".

```

'GenerateCoSimBlock' — Generate HDL Cosimulation block

```

'off' (default) | 'on'

Generate an HDL Cosimulation block so you can simulate the DUT in Simulink with an HDL simulator.

For more information, see "GenerateCoSimBlock".

```

'GenerateCoSimModel' — Generate HDL Cosimulation model

'ModelSim' (default) | 'Incisive'

```

Generate a model containing an HDL Cosimulation block for the specified HDL simulator.

For more information, see "GenerateCoSimModel".

## **Coding Style**

```

'UseVerilogTimescale' — Generate 'timescale compiler directives

'on' (default) | 'off'

```

For more information, see "UseVerilogTimescale".

```

'DateComment' — Include time stamp in header 'on' (default) | 'off'

```

For more information, see "DateComment".

```

'InlineConfigurations' - Include VHDL configurations

'on' (default) | 'off'

```

For more information, see "InlineConfigurations".

```

'ScalarizePorts' — Flatten vector ports into scalar ports

'off' (default) | 'on'

```

For more information, see "ScalarizePorts".

### **Script Generation**

```

'HDLCompileInit' - Compilation script initialization string

'vlib work\n' (default) | string

```

For more information, see "HDLCompileInit".

'HDLCompileTerm' — Compilation script termination string

For more information, see "HDLCompileTerm".

```

'HDLCompileFilePostfix' — Postfix for compilation script file name

'_compile.do' (default) | string

```

For more information, see "HDLCompileFilePostfix".

'HDLCompileVerilogCmd' - Verilog compilation command

'vlog %s %s\n' (default) | string

Verilog compilation command, specified as a string. The SimulatorFlags name-value pair specifies the first argument, and the module name specifies the second argument.

For more information, see "HDLCompileVerilogCmd".

#### 'HDLCompileVHDLCmd' - VHDL compilation command

'vcom %s %s\n' (default) | string

VHDL compilation command, specified as a string. The SimulatorFlags name-value pair specifies the first argument, and the entity name specifies the second argument.

For more information, see "HDLCompileVerilogCmd".

```

'HDLSimCmd' - HDL simulation command

'vsim -novopt %s.%s\n' (default) | string

```

The HDL simulation command, specified as a string.

For more information, see "HDLSimCmd".

```

'HDLSimInit' - HDL simulation script initialization string

['onbreak resume\n', 'onerror resume\n'] (default) | string

```

Initialization for the HDL simulation script, specified as a string.

For more information, see "HDLSimInit".

```

'HDLSimTerm' — HDL simulation script termination string

'run -all' (default) | string

```

The termination string for the HDL simulation command.

For more information, see "HDLSimTerm".

```

'HDLSimFilePostfix' — Postscript for HDL simulation script

'_sim.do' (default) | string

```

For more information, see "HDLSimFilePostfix".

'HDLSimViewWaveCmd' — HDL simulation waveform viewing command 'add wave sim:%s\n' (default) | string

Waveform viewing command, specified as a string. The implicit argument adds the signal paths for the DUT top-level input, output, and output reference signals.

For more information, see "HDLSimViewWaveCmd".

### Port Names and Types

'ClockEnableInputPort' - Clock enable input port name

'clk\_enable' (default) | string

Clock enable input port name, specified as a string.

For more information, see "ClockEnableInputPort".

'ClockEnableOutputPort' - Clock enable output port name

'ce\_out' (default) | string

Clock enable output port name, specified as a string.

For more information, see "ClockEnableOutputPort".

'ClockInputPort' - Clock input port name

'clk' (default) | string

Clock input port name, specified as a string.

For more information, see "ClockInputPort".

'ResetInputPort' - Reset input port name

'reset' (default) | string

Reset input port name, specified as a string.

For more information, see "ResetInputPort".

### File and Variable Names

'VerilogFileExtension' - Verilog file extension

'.v' (default) | string

For more information, see "VerilogFileExtension".

'VHDLFileExtension' - VHDL file extension

'.vhd' (default) | string

For more information, see "VHDLFileExtension".

```

'VHDLArchitectureName' — VHDL architecture name

'rtl' (default) | string

```

For more information, see "VHDLArchitectureName".

'VHDLLibraryName' — VHDL library name 'work' (default) | string

For more information, see "VHDLLibraryName".

'SplitEntityFilePostfix' - Postfix for VHDL entity file names

'\_entity' (default) | string

For more information, see "SplitEntityFilePostfix".

'SplitArchFilePostfix' - Postfix for VHDL architecture file names

'\_arch' (default) | string

For more information, see "SplitArchFilePostfix".

'PackagePostfix' - Postfix for package file name

'\_pkg' (default) | string

For more information, see "PackagePostfix".

'ComplexImagPostfix' - Postfix for imaginary part of complex signal

'\_im' (default) | string

For more information, see "ComplexImagPostfix".

'ComplexRealPostfix' - Postfix for imaginary part of complex signal names

'\_re' (default) | string

For more information, see "ComplexRealPostfix".

'EnablePrefix' — Prefix for internal enable signals

'enb' (default) | string

Prefix for internal clock enable and control flow enable signals, specified as a string.

For more information, see "EnablePrefix".

See Also makehdl

# Supported Blocks

# 1-D Lookup Table

1-D Lookup Table implementations, properties, and restrictions for HDL code generation

# Description

The 1-D Lookup Table block is a one-dimensional version of the n-D Lookup Table block. For HDL code generation information, see n-D Lookup Table.

# 2-D Lookup Table

2-D Lookup Table implementations, properties, and restrictions for HDL code generation

# Description

The 2-D Lookup Table block is a two-dimensional version of the n-D Lookup Table block. For HDL code generation information, see n-D Lookup Table.

# Abs

Abs implementations, properties, and restrictions for HDL code generation

# Description

The Abs block is available with Simulink.

For information on the Simulink simulation behavior and block parameters, see Abs.

# **HDL Implementations**

This block has a single default HDL architecture.

# **HDL Block Properties**

### ConstrainedOutputPipeline

Number of registers to place at the outputs. Distributed pipelining does not redistribute these registers. The default is 0. See also "ConstrainedOutputPipeline".

### InputPipeline

Number of input pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is 0. See also "InputPipeline".

### OutputPipeline

Number of output pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is 0. See also "OutputPipeline".

# Add

Add implementations, properties, and restrictions for HDL code generation

## Description

The Add block is available with Simulink.

For information on the Simulink simulation behavior and block parameters, see Add.

# **HDL Implementations**

The default Linear implementation generates a chain of N operations (adders) for N inputs.

# **HDL Block Properties**

### **ConstrainedOutputPipeline**

Number of registers to place at the outputs. Distributed pipelining does not redistribute these registers. The default is 0. See also "ConstrainedOutputPipeline".

### InputPipeline

Number of input pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is 0. See also "InputPipeline".

### **OutputPipeline**

Number of output pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is 0. See also "OutputPipeline".

# **Complex Data Support**

The default Linear implementation supports complex data.

# Assertion

Assertion implementations, properties, and restrictions for HDL code generation

# Description

The Assertion block is available with Simulink.

For information on the Simulink simulation behavior and block parameters, see Assertion.

# **HDL Implementations**

When you use this block in your model, HDL Coder does not generate HDL code for it.

# Assignment

Assignment implementations, properties, and restrictions for HDL code generation

## Description

The Assignment block is available with Simulink.

For information on the Simulink simulation behavior and block parameters, see Assignment.

## **HDL Implementations**

This block has a single default HDL architecture.

## **HDL Block Properties**

### **ConstrainedOutputPipeline**

Number of registers to place at the outputs. Distributed pipelining does not redistribute these registers. The default is 0. See also "ConstrainedOutputPipeline".

### InputPipeline

Number of input pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is 0. See also "InputPipeline".

### **OutputPipeline**

Number of output pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is 0. See also "OutputPipeline".

## **Complex Data Support**

This block supports code generation for complex signals.

# Atomic Subsystem

Atomic Subsystem implementations, properties, and restrictions for HDL code generation

## Description

The Atomic Subsystem block is available with Simulink.

For information on the Simulink simulation behavior and block parameters, see Atomic Subsystem.

| Implementation   | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module (default) | Generate code for the subsystem and the blocks within the subsystem.                                                                                                                                                                                                                                                                                                                                                         |